Loading...

Searching...

No Matches

core_cm0plus.h File Reference

CMSIS Cortex-M0+ Core Peripheral Access Layer Header File. More...

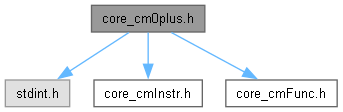

Include dependency graph for core_cm0plus.h:

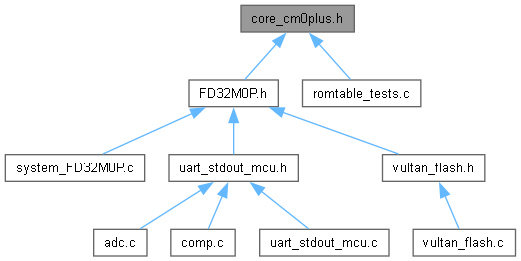

This graph shows which files directly or indirectly include this file:

Data Structures | |

| union | APSR_Type |

| Union type to access the Application Program Status Register (APSR). More... | |

| union | IPSR_Type |

| Union type to access the Interrupt Program Status Register (IPSR). More... | |

| union | xPSR_Type |

| Union type to access the Special-Purpose Program Status Registers (xPSR). More... | |

| union | CONTROL_Type |

| Union type to access the Control Registers (CONTROL). More... | |

| struct | NVIC_Type |

| Structure type to access the Nested Vectored Interrupt Controller (NVIC). More... | |

| struct | SCB_Type |

| Structure type to access the System Control Block (SCB). More... | |

| struct | SysTick_Type |

| Structure type to access the System Timer (SysTick). More... | |

| struct | APSR_Type.b |

| struct | IPSR_Type.b |

| struct | xPSR_Type.b |

| struct | CONTROL_Type.b |

Functions | |

| __STATIC_INLINE void | NVIC_EnableIRQ (IRQn_Type IRQn) |

| Enable External Interrupt. | |

| __STATIC_INLINE void | NVIC_DisableIRQ (IRQn_Type IRQn) |

| Disable External Interrupt. | |

| __STATIC_INLINE uint32_t | NVIC_GetPendingIRQ (IRQn_Type IRQn) |

| Get Pending Interrupt. | |

| __STATIC_INLINE void | NVIC_SetPendingIRQ (IRQn_Type IRQn) |

| Set Pending Interrupt. | |

| __STATIC_INLINE void | NVIC_ClearPendingIRQ (IRQn_Type IRQn) |

| Clear Pending Interrupt. | |

| __STATIC_INLINE void | NVIC_SetPriority (IRQn_Type IRQn, uint32_t priority) |

| Set Interrupt Priority. | |

| __STATIC_INLINE uint32_t | NVIC_GetPriority (IRQn_Type IRQn) |

| Get Interrupt Priority. | |

| __STATIC_INLINE void | NVIC_SystemReset (void) |

| System Reset. | |

| __STATIC_INLINE uint32_t | SysTick_Config (uint32_t ticks) |

| System Tick Configuration. | |

Detailed Description

CMSIS Cortex-M0+ Core Peripheral Access Layer Header File.

- Version

- V3.20

- Date

- 25. February 2013

- Note

Macro Definition Documentation

◆ __CORE_CM0PLUS_H_GENERIC

| #define __CORE_CM0PLUS_H_GENERIC |