Loading...

Searching...

No Matches

config_id.h File Reference

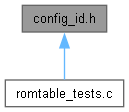

This graph shows which files directly or indirectly include this file:

Macros | |

| #define | TEST_PASS 0 |

| #define | TEST_FAIL 1 |

| #define | MCU_CPU_NAME "Cortex-M0+" |

| #define | MCU_CPU_ID_VALUE 0x410cc601 |

| #define | MCU_DP_IDR_VALUE 0x6BA02477 |

| #define | MCU_AP_IDR_VALUE 0x84770001 |

| #define | MCU_AP_BASE_VALUE 0xF0000003 |

| #define | CORESIGHT_CID0 0x0D |

| #define | CORESIGHT_CID1_tbl 0x10 |

| #define | CORESIGHT_CID1_dbg 0x90 |

| #define | CORESIGHT_CID1_mem 0xE0 |

| #define | CORESIGHT_CID1_prm 0xF0 |

| #define | CORESIGHT_CID2 0x05 |

| #define | CORESIGHT_CID3 0xB1 |

| #define | ARM_JEP_ID 0x3B |

| #define | ARM_JEP_CONT 0x4 |

| #define | CORTEXM0_CPUID 0x410cc200 |

| #define | CM0_CPU_PART 0x471 |

| #define | CM0_SCS_PART 0x008 |

| #define | CM0_DWT_PART 0x00A |

| #define | CM0_BPU_PART 0x00B |

| #define | CM0_CPU_PART 0x471 |

| #define | CM0_CSI_PART 0x4C2 |

| #define | CS_CTI_PART 0x906 |

| #define | CM0_DAP_DP_PART 0xBB |

| #define | CM0_ROM_REV 0x0 |

| #define | CM0_SCS_REV 0x0 |

| #define | CM0_DWT_REV 0x0 |

| #define | CM0_BPU_REV 0x0 |

| #define | CM0_ROM_ECO 0x0 |

| #define | CM0_SCS_ECO 0x0 |

| #define | CM0_DWT_ECO 0x0 |

| #define | CM0_BPU_ECO 0x0 |

| #define | CORTEXM0DAP_JTAG_TAPID 0x0BA01477 |

| #define | CORTEXM0DAP_JTAG_DPIDR 0x0BB11477 |

| #define | CORTEXM0DAP_SW_DPIDR 0x0BB11477 |

| #define | CORTEXM0DAP_AP_IDR 0x04770021 |

| #define | CORTEXM0_ROM_PID3 0x00 |

| #define | CORTEXM0_SCS_PID3 0x00 |

| #define | CORTEXM0_DWT_PID3 0x00 |

| #define | CORTEXM0_BPU_PID3 0x00 |

| #define | CORTEXM0PLUS_CPUID (0x410cc601 ^ (EXPECTED_ECOREVNUM & 0x0000000F)) |

| #define | CM0P_CPU_PART 0x4C0 |

| #define | CM0P_SCS_PART 0x008 |

| #define | CM0P_DWT_PART 0x00A |

| #define | CM0P_BPU_PART 0x00B |

| #define | CM0P_MTB_PART 0x932 |

| #define | CM0P_CSI_PART 0x4C1 |

| #define | CM0P_CTI_PART 0x9A6 |

| #define | CM0P_DAP_DP_PART 0xBC |

| #define | CM0P_ROM_REV 0x0 |

| #define | CM0P_SCS_REV 0x0 |

| #define | CM0P_DWT_REV 0x0 |

| #define | CM0P_BPU_REV 0x0 |

| #define | CM0P_MTB_REV 0x1 |

| #define | CM0P_DAP_DP_REV (0x0 ^ ((EXPECTED_ECOREVNUM & 0x0F000000) >> 24)) |

| #define | CM0P_DAP_AP_REV (0x0 ^ ((EXPECTED_ECOREVNUM & 0x00F00000) >> 20)) |

| #define | CM0P_ROM_ECO ((EXPECTED_ECOREVNUM & 0x000F0000) >> 16) |

| #define | CM0P_SCS_ECO ((EXPECTED_ECOREVNUM & 0x0000F000) >> 12) |

| #define | CM0P_DWT_ECO ((EXPECTED_ECOREVNUM & 0x00000F00) >> 8) |

| #define | CM0P_BPU_ECO ((EXPECTED_ECOREVNUM & 0x000000F0) >> 4) |

| #define | CM0P_MTB_ECO ((EXPECTED_ECOREVNUM & 0xF0000000) >> 28) |

| #define | CM0P_DAP_JTAG_TAPID (0x0BA01477 | (CM0P_DAP_DP_REV << 28)) |

| #define | CM0P_DAP_JTAG_DPIDR (0x0BC11477 | (CM0P_DAP_DP_REV << 28)) |

| #define | CM0P_DAP_SW_DPIDR (0x0BC11477 | (CM0P_DAP_DP_REV << 28)) |

| #define | CM0P_DAP_SWMD_DPIDR (0x0BC12477 | (CM0P_DAP_DP_REV << 28)) |

| #define | CM0P_DAP_APIDR (0x04770031 | (CM0P_DAP_AP_REV << 28)) |

| #define | EXPECTED_BE 0 |

| #define | EXPECTED_BKPT 4 |

| #define | EXPECTED_DBG 1 |

| #define | EXPECTED_NUMIRQ 32 |

| #define | EXPECTED_SMUL 0 |

| #define | EXPECTED_SYST 1 |

| #define | EXPECTED_WPT 2 |

| #define | EXPECTED_SIMPLE_CHECK 0 |

| #define | EXPECTED_STCALIB 0x1028B0A |

| #define | EXPECTED_BASEADDR 0xF0000003 |

| #define | EXPECTED_JTAGnSW 0 |

| #define | EXPECTED_CUST_JEP_ID 0x00 |

| #define | EXPECTED_CUST_JEP_CONT 0x0 |

| #define | EXPECTED_CUST_PART 0x000 |

| #define | EXPECTED_CUST_REV 0x0 |

| #define | EXPECTED_CUST_REVAND 0x0 |

| #define | EXPECTED_ECOREVNUM 0x00000000 |

| #define | EXPECTED_CSI 0 |

| #define | EXPECTED_CTI 0 |

| #define | EXPECTED_IOP 0 |

| #define | EXPECTED_IRQDIS 0x00000000 |

| #define | EXPECTED_MPU 8 |

| #define | EXPECTED_USER 1 |

| #define | EXPECTED_VTOR 1 |

| #define | EXPECTED_WIC 1 |

| #define | EXPECTED_WICLINES 34 |

| #define | EXPECTED_SWMD 0 |

| #define | EXPECTED_INSTANCEID 0x0 |

| #define | EXPECTED_TREVISION 0x0 |

| #define | EXPECTED_TPARTNO 0x0000 |

| #define | EXPECTED_TDESIGNER 0x000 |

| #define | EXPECTED_MTB 0 |

| #define | EXPECTED_MTB_BASEADDR 0xF0210000 |

| #define | EXPECTED_MTB_AWIDTH 16 |

Macro Definition Documentation

◆ TEST_PASS

| #define TEST_PASS 0 |

Referenced by main().

◆ TEST_FAIL

| #define TEST_FAIL 1 |

◆ MCU_CPU_NAME

| #define MCU_CPU_NAME "Cortex-M0+" |

Referenced by main().

◆ MCU_CPU_ID_VALUE

| #define MCU_CPU_ID_VALUE 0x410cc601 |

◆ MCU_DP_IDR_VALUE

| #define MCU_DP_IDR_VALUE 0x6BA02477 |

◆ MCU_AP_IDR_VALUE

| #define MCU_AP_IDR_VALUE 0x84770001 |

◆ MCU_AP_BASE_VALUE

| #define MCU_AP_BASE_VALUE 0xF0000003 |

◆ CORESIGHT_CID0

| #define CORESIGHT_CID0 0x0D |

◆ CORESIGHT_CID1_tbl

| #define CORESIGHT_CID1_tbl 0x10 |

◆ CORESIGHT_CID1_dbg

| #define CORESIGHT_CID1_dbg 0x90 |

◆ CORESIGHT_CID1_mem

| #define CORESIGHT_CID1_mem 0xE0 |

◆ CORESIGHT_CID1_prm

| #define CORESIGHT_CID1_prm 0xF0 |

◆ CORESIGHT_CID2

| #define CORESIGHT_CID2 0x05 |

◆ CORESIGHT_CID3

| #define CORESIGHT_CID3 0xB1 |

◆ ARM_JEP_ID

| #define ARM_JEP_ID 0x3B |

Referenced by GetCoreSightIDs().

◆ ARM_JEP_CONT

| #define ARM_JEP_CONT 0x4 |

Referenced by GetCoreSightIDs().

◆ CORTEXM0_CPUID

| #define CORTEXM0_CPUID 0x410cc200 |

◆ CM0_CPU_PART [1/2]

| #define CM0_CPU_PART 0x471 |

◆ CM0_SCS_PART

| #define CM0_SCS_PART 0x008 |

◆ CM0_DWT_PART

| #define CM0_DWT_PART 0x00A |

◆ CM0_BPU_PART

| #define CM0_BPU_PART 0x00B |

◆ CM0_CPU_PART [2/2]

| #define CM0_CPU_PART 0x471 |

◆ CM0_CSI_PART

| #define CM0_CSI_PART 0x4C2 |

◆ CS_CTI_PART

| #define CS_CTI_PART 0x906 |

◆ CM0_DAP_DP_PART

| #define CM0_DAP_DP_PART 0xBB |

◆ CM0_ROM_REV

| #define CM0_ROM_REV 0x0 |

◆ CM0_SCS_REV

| #define CM0_SCS_REV 0x0 |

◆ CM0_DWT_REV

| #define CM0_DWT_REV 0x0 |

◆ CM0_BPU_REV

| #define CM0_BPU_REV 0x0 |

◆ CM0_ROM_ECO

| #define CM0_ROM_ECO 0x0 |

◆ CM0_SCS_ECO

| #define CM0_SCS_ECO 0x0 |

◆ CM0_DWT_ECO

| #define CM0_DWT_ECO 0x0 |

◆ CM0_BPU_ECO

| #define CM0_BPU_ECO 0x0 |

◆ CORTEXM0DAP_JTAG_TAPID

| #define CORTEXM0DAP_JTAG_TAPID 0x0BA01477 |

◆ CORTEXM0DAP_JTAG_DPIDR

| #define CORTEXM0DAP_JTAG_DPIDR 0x0BB11477 |

◆ CORTEXM0DAP_SW_DPIDR

| #define CORTEXM0DAP_SW_DPIDR 0x0BB11477 |

◆ CORTEXM0DAP_AP_IDR

| #define CORTEXM0DAP_AP_IDR 0x04770021 |

◆ CORTEXM0_ROM_PID3

| #define CORTEXM0_ROM_PID3 0x00 |

◆ CORTEXM0_SCS_PID3

| #define CORTEXM0_SCS_PID3 0x00 |

◆ CORTEXM0_DWT_PID3

| #define CORTEXM0_DWT_PID3 0x00 |

◆ CORTEXM0_BPU_PID3

| #define CORTEXM0_BPU_PID3 0x00 |

◆ CORTEXM0PLUS_CPUID

| #define CORTEXM0PLUS_CPUID (0x410cc601 ^ (EXPECTED_ECOREVNUM & 0x0000000F)) |

◆ CM0P_CPU_PART

| #define CM0P_CPU_PART 0x4C0 |

◆ CM0P_SCS_PART

| #define CM0P_SCS_PART 0x008 |

◆ CM0P_DWT_PART

| #define CM0P_DWT_PART 0x00A |

◆ CM0P_BPU_PART

| #define CM0P_BPU_PART 0x00B |

◆ CM0P_MTB_PART

| #define CM0P_MTB_PART 0x932 |

◆ CM0P_CSI_PART

| #define CM0P_CSI_PART 0x4C1 |

◆ CM0P_CTI_PART

| #define CM0P_CTI_PART 0x9A6 |

◆ CM0P_DAP_DP_PART

| #define CM0P_DAP_DP_PART 0xBC |

◆ CM0P_ROM_REV

| #define CM0P_ROM_REV 0x0 |

◆ CM0P_SCS_REV

| #define CM0P_SCS_REV 0x0 |

◆ CM0P_DWT_REV

| #define CM0P_DWT_REV 0x0 |

◆ CM0P_BPU_REV

| #define CM0P_BPU_REV 0x0 |

◆ CM0P_MTB_REV

| #define CM0P_MTB_REV 0x1 |

◆ CM0P_DAP_DP_REV

| #define CM0P_DAP_DP_REV (0x0 ^ ((EXPECTED_ECOREVNUM & 0x0F000000) >> 24)) |

◆ CM0P_DAP_AP_REV

| #define CM0P_DAP_AP_REV (0x0 ^ ((EXPECTED_ECOREVNUM & 0x00F00000) >> 20)) |

◆ CM0P_ROM_ECO

| #define CM0P_ROM_ECO ((EXPECTED_ECOREVNUM & 0x000F0000) >> 16) |

◆ CM0P_SCS_ECO

| #define CM0P_SCS_ECO ((EXPECTED_ECOREVNUM & 0x0000F000) >> 12) |

◆ CM0P_DWT_ECO

| #define CM0P_DWT_ECO ((EXPECTED_ECOREVNUM & 0x00000F00) >> 8) |

◆ CM0P_BPU_ECO

| #define CM0P_BPU_ECO ((EXPECTED_ECOREVNUM & 0x000000F0) >> 4) |

◆ CM0P_MTB_ECO

| #define CM0P_MTB_ECO ((EXPECTED_ECOREVNUM & 0xF0000000) >> 28) |

◆ CM0P_DAP_JTAG_TAPID

| #define CM0P_DAP_JTAG_TAPID (0x0BA01477 | (CM0P_DAP_DP_REV << 28)) |

◆ CM0P_DAP_JTAG_DPIDR

| #define CM0P_DAP_JTAG_DPIDR (0x0BC11477 | (CM0P_DAP_DP_REV << 28)) |

◆ CM0P_DAP_SW_DPIDR

| #define CM0P_DAP_SW_DPIDR (0x0BC11477 | (CM0P_DAP_DP_REV << 28)) |

◆ CM0P_DAP_SWMD_DPIDR

| #define CM0P_DAP_SWMD_DPIDR (0x0BC12477 | (CM0P_DAP_DP_REV << 28)) |

◆ CM0P_DAP_APIDR

| #define CM0P_DAP_APIDR (0x04770031 | (CM0P_DAP_AP_REV << 28)) |

◆ EXPECTED_BE

| #define EXPECTED_BE 0 |

◆ EXPECTED_BKPT

| #define EXPECTED_BKPT 4 |

◆ EXPECTED_DBG

| #define EXPECTED_DBG 1 |

Referenced by main().

◆ EXPECTED_NUMIRQ

| #define EXPECTED_NUMIRQ 32 |

◆ EXPECTED_SMUL

| #define EXPECTED_SMUL 0 |

◆ EXPECTED_SYST

| #define EXPECTED_SYST 1 |

◆ EXPECTED_WPT

| #define EXPECTED_WPT 2 |

◆ EXPECTED_SIMPLE_CHECK

| #define EXPECTED_SIMPLE_CHECK 0 |

◆ EXPECTED_STCALIB

| #define EXPECTED_STCALIB 0x1028B0A |

◆ EXPECTED_BASEADDR

| #define EXPECTED_BASEADDR 0xF0000003 |

◆ EXPECTED_JTAGnSW

| #define EXPECTED_JTAGnSW 0 |

Referenced by main().

◆ EXPECTED_CUST_JEP_ID

| #define EXPECTED_CUST_JEP_ID 0x00 |

Referenced by CheckDisplayPID().

◆ EXPECTED_CUST_JEP_CONT

| #define EXPECTED_CUST_JEP_CONT 0x0 |

Referenced by CheckDisplayPID().

◆ EXPECTED_CUST_PART

| #define EXPECTED_CUST_PART 0x000 |

◆ EXPECTED_CUST_REV

| #define EXPECTED_CUST_REV 0x0 |

◆ EXPECTED_CUST_REVAND

| #define EXPECTED_CUST_REVAND 0x0 |

◆ EXPECTED_ECOREVNUM

| #define EXPECTED_ECOREVNUM 0x00000000 |

◆ EXPECTED_CSI

| #define EXPECTED_CSI 0 |

◆ EXPECTED_CTI

| #define EXPECTED_CTI 0 |

◆ EXPECTED_IOP

| #define EXPECTED_IOP 0 |

◆ EXPECTED_IRQDIS

| #define EXPECTED_IRQDIS 0x00000000 |

◆ EXPECTED_MPU

| #define EXPECTED_MPU 8 |

◆ EXPECTED_USER

| #define EXPECTED_USER 1 |

◆ EXPECTED_VTOR

| #define EXPECTED_VTOR 1 |

◆ EXPECTED_WIC

| #define EXPECTED_WIC 1 |

◆ EXPECTED_WICLINES

| #define EXPECTED_WICLINES 34 |

◆ EXPECTED_SWMD

| #define EXPECTED_SWMD 0 |

◆ EXPECTED_INSTANCEID

| #define EXPECTED_INSTANCEID 0x0 |

◆ EXPECTED_TREVISION

| #define EXPECTED_TREVISION 0x0 |

◆ EXPECTED_TPARTNO

| #define EXPECTED_TPARTNO 0x0000 |

◆ EXPECTED_TDESIGNER

| #define EXPECTED_TDESIGNER 0x000 |

◆ EXPECTED_MTB

| #define EXPECTED_MTB 0 |

◆ EXPECTED_MTB_BASEADDR

| #define EXPECTED_MTB_BASEADDR 0xF0210000 |

◆ EXPECTED_MTB_AWIDTH

| #define EXPECTED_MTB_AWIDTH 16 |