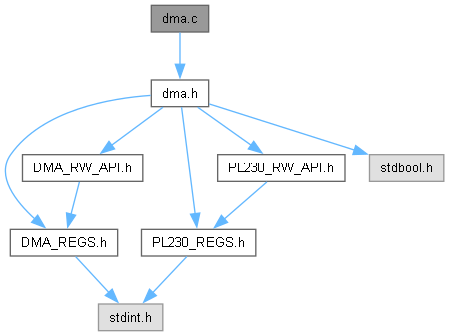

#include "dma.h"

Functions | |

| void | dma_init (PL230_REGS_s *PL230_REGS, uint32_t base_ptr_address) |

| This function initalizes the dma, waits if there is any current transaction, set dma structure addressm disable all the channels and enables the controller. | |

| void | dma_channel_cfg (DMA_REGS_s *DMA_REGS, PL230_REGS_s *PL230_REGS, dma_channel_cfg_t *dma_channel_cfg, DMA_CHANNEL_E channel) |

| void | dma_channel_en_set (PL230_REGS_s *PL230_REGS, DMA_CHANNEL_E channel) |

| uint8_t | dma_channel_en_get (PL230_REGS_s *PL230_REGS, DMA_CHANNEL_E channel) |

| void | dma_channel_sw_trig (PL230_REGS_s *PL230_REGS, DMA_CHANNEL_E channel) |

| void | dma_channel_priority_cfg (DMA_REGS_s *DMA_REGS, DMA_ARBITRATION_DMA_RR_EN_E mode, uint16_t round_robin_mask) |

| This function set the dma arbitration. | |

| bool | dma_is_idle (PL230_REGS_s *PL230_REGS) |

| This function check if dma fsm is in idle/stalled/done state. | |

| void | dma_channel_en_clr (PL230_REGS_s *PL230_REGS, DMA_CHANNEL_E channel) |

Function Documentation

◆ dma_channel_cfg()

| void dma_channel_cfg | ( | DMA_REGS_s * | DMA_REGS, |

| PL230_REGS_s * | PL230_REGS, | ||

| dma_channel_cfg_t * | dma_channel_cfg, | ||

| DMA_CHANNEL_E | channel ) |

References PL230_REGS_s::ALT_CTRL_BASE_PTR, DMA_REGS_s::CFG_0, DMA_REGS_s::CFG_1, dma_mem_channel_cfg_t::ctrl, PL230_REGS_s::CTRL_BASE_PTR, dma_mem_ctrl_cfg_t::cycle_ctrl, dma_channel_cfg(), DMA_SRC_INC_NO_INCR, DMA_STRIDE_MODE_LOOKUP_DST_ADDR, DMA_STRIDE_MODE_LOOKUP_SRC_ADDR, dma_mem_ctrl_cfg_t::dst_inc, dma_mem_ctrl_cfg_t::dst_prot_ctrl, dma_mem_ctrl_cfg_t::dst_size, DMA_REGS_s::FILL_MODE, DMA_REGS_s::FILL_MODE_CFG, dma_mem_ctrl_cfg_t::n_minus_1, dma_mem_ctrl_cfg_t::next_useburst, DMA_REPEATED_TRANSFER_ALTERNATE_SEL_u::packed_w, PL230_ALT_CTRL_BASE_PTR_u::packed_w, PL230_CTRL_BASE_PTR_u::packed_w, dma_mem_ctrl_cfg_t::r_power, dma_mem_channel_cfg_t::rdp, DMA_REGS_s::REPEATED_TRANSFER_ALTERNATE_SEL, DMA_REGS_s::REPEATED_TRANSFER_CHNL_0, DMA_REGS_s::REPEATED_TRANSFER_EN, dma_mem_channel_cfg_t::rsp, dma_mem_ctrl_cfg_t::src_inc, dma_mem_ctrl_cfg_t::src_prot_ctrl, dma_mem_ctrl_cfg_t::src_size, DMA_REGS_s::STRIDE_MODE, DMA_REGS_s::STRIDE_MODE_CFG_0, DMA_REGS_s::STRIDE_MODE_CFG_1, and DMA_REGS_s::STRIDE_MODE_CFG_2.

Referenced by dma_channel_cfg(), and dma_channel_cfg().

◆ dma_channel_en_set()

| void dma_channel_en_set | ( | PL230_REGS_s * | PL230_REGS, |

| DMA_CHANNEL_E | channel ) |

References PL230_REGS_s::CHNL_ENABLE_SET, and PL230_CHNL_ENABLE_SET_u::packed_w.

◆ dma_channel_en_get()

| uint8_t dma_channel_en_get | ( | PL230_REGS_s * | PL230_REGS, |

| DMA_CHANNEL_E | channel ) |

References PL230_REGS_s::CHNL_ENABLE_SET, and PL230_CHNL_ENABLE_SET_u::packed_w.

◆ dma_channel_sw_trig()

| void dma_channel_sw_trig | ( | PL230_REGS_s * | PL230_REGS, |

| DMA_CHANNEL_E | channel ) |

References PL230_REGS_s::CHNL_SW_REQUEST, and PL230_CHNL_SW_REQUEST_u::packed_w.

◆ dma_channel_en_clr()

| void dma_channel_en_clr | ( | PL230_REGS_s * | PL230_REGS, |

| DMA_CHANNEL_E | channel ) |

References PL230_REGS_s::CHNL_ENABLE_CLR, and PL230_CHNL_ENABLE_CLR_u::packed_w.